设计一种新的基于CMOS的电子传感接收电路,并介绍了电子传感接收电路设计方案。依据设计方案,选用源级负反馈电感匹配结构对低噪声放大器的基本电路结构进行设计;为达到性能指标和降低功耗,混频器電路结构选用无源双平衡混频器结构;为了降低整个电子传感接收电路的能耗,令无源双平衡混频器的开关MOS管在无电流偏置的情况下运行。给出了复数滤波器设计的基本思想,通过反馈系统对编程增益放大器的增益进行管理,实现可编程放大器的设计。实验结果表明,所设计电路性能符合设计要求。

设计一种新的基于CMOS的电子传感接收电路,并介绍了电子传感接收电路设计方案。依据设计方案,选用源级负反馈电感匹配结构对低噪声放大器的基本电路结构进行设计;为达到性能指标和降低功耗,混频器電路结构选用无源双平衡混频器结构;为了降低整个电子传感接收电路的能耗,令无源双平衡混频器的开关MOS管在无电流偏置的情况下运行。给出了复数滤波器设计的基本思想,通过反馈系统对编程增益放大器的增益进行管理,实现可编程放大器的设计。实验结果表明,所设计电路性能符合设计要求。

关键词: CMOS; 电子传感接收电路; 复数滤波器; 无源双平衡混频器; 编程增益放大器

中图分类号: TN99⁃34; TP393 文献标识码: A 文章编号: 1004⁃373X(2017)18⁃0124⁃03

Design and implementation electronic sensing receiving circuit based on CMOS

QIU Xiaoqun1, ZHANG Gang2

(1. School of Electronic and Information Engineering, Zhuhai City Polytechnic, Zhuhai 519090, China;

2. School of Automation, Guangdong University of Technology, Guangzhou 510006, China)

Abstract: The current electronic sensing receiving circuit has high energy consumption, and its performance parameters can′t meet the design requirements. Therefore, a new electronic sensing receiving circuit based on CMOS was designed. Its design scheme is introduced in this paper. According to this design scheme, the source⁃level negative feedback inductance matching structure is selected to design the basic circuit structure of the low⁃noise amplifier. In order to reach the performance index and reduce the power consumption, the structure of passive double balanced mixer is chosen for the circuit structure of mixer. For reducing the energy consumption of the whole electronic sensing receiving circuit, the switch MOS tube of passive double balanced mixer operates without current bias. The basic design thought of complex filter is given. The gain of the programmable gain amplifier is controlled by feedback system to realize the design of programmable amplifier. The experimental results show that the circuit performance meets the design requirements.

Keywords: CMOS; electronic sensing receiving circuit; complex filter; passive double balanced mixer; programmable gain amplifier

随着科技的逐渐发展,无线传感网络技术被广泛应用于军事、医疗和工业等领域。而电子传感接收电路是整个无线传感网络中的重要模块,对整个系统的性能指标产生直接影响[1]。因此,设计一种有效的电子传感接收电路具有重要意义。

1 基于CMOS的电子传感接收电路的设计与实现

1.1 电子传感接收电路设计方案

电子传感接收电路的基本思想如下:低频信号经天线和滤波处理后,通过低噪声放大器完成对其的放大处理,利用Mixer混频和下变频对中频信号进行采集 [2]。与一般的接收电路相比,电子传感接收电路结构需对对应镜象频率干扰进行滤除,通常情况下,低中频信号经下变频后被引入复数滤波器,其不仅可实现镜象干扰的滤除,还可准确判断有用信道。然后经自动增益调控把信号保持在解调器所需功率值范围内,通过A/D转化完成对其的基带处理。

本节选用低中频电子传感接收电路结构,其将中频频率设计在较低的频率上,滤除噪声、失真和偏移等干扰,结构较为简单,易于集成,能够达到接收电路前端与基带处理集成的目的[3],被广泛应用于各种通信系统中。

1.2 CMOS低噪声放大器的基本电路结构设计

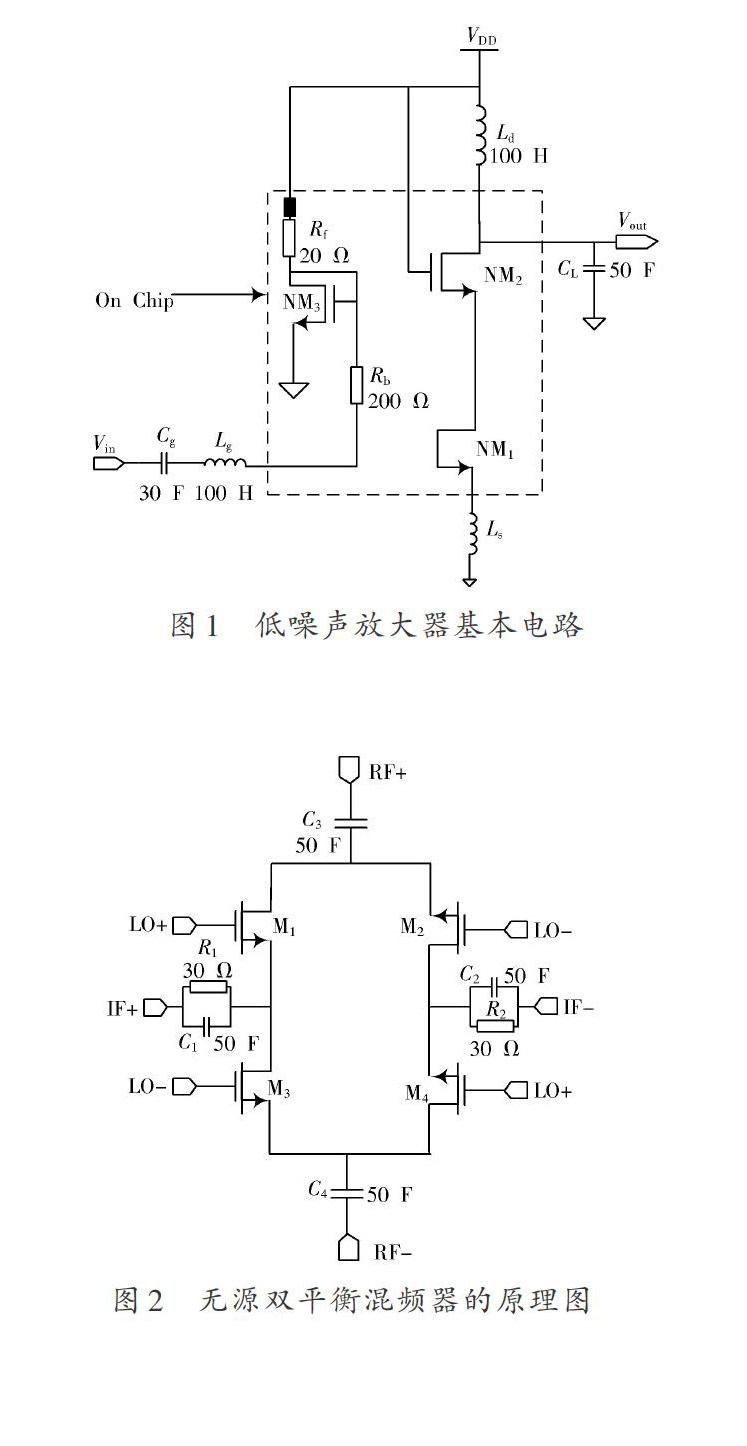

依据设计方案,本节选用源级负反馈电感匹配结构对CMOS低噪声放大器的基本电路结构进行设计,设计的结构图如图1所示。

图1 低噪声放大器基本电路

图1中,NM3与NM1构成了电流镜,为NM1提供偏置电流。为了降低能耗,在设计时令NM3的宽度[4]低于NM1。Rb的阻值相对较大,能够大大降低电阻的等效噪声电流;Cg代表隔直电容;Ls不僅能够和输入阻抗匹配,还能够与Lg和输入端的等效电容结合在一起构成输入谐振网络;Ld与输出端的等效电容CL谐振,也可将其看作输出匹配网络。因为设计的放大器是窄带放大器,输入与输出谐振网络均处于工作频率中,以增强功率增益;NM2主要用于降低NM1栅漏电容的密勒效应,增加隔离度,尽可能地减少输入与输出谐振电路之间产生的作用。

1.3 混频器电路设计

为了达到性能指标和低功耗的目的,混频器电路结构选用无源双平衡混频器结构,其电路见图2。

图2 无源双平衡混频器的原理图

图2中,将所设计电子传感接收电路中的射频信号由MOS管的源极输入,令本振信号和MOS管的栅极直接相连,以管理MOS管的开关状态,达到混频的目的,通过MOS管的漏极输出中频信号,令RC滤波网络与输出端连接在一起,通过经验得到一个合理的RC值,以抑制经电容耦合的射频信号,各器件值如图2所示[5]。

1.4 复数滤波器设计

复数滤波器的基本思想如下:设计一种依据OTA的三阶巴特沃斯低通滤波器,其带宽是1 MHz,对得到的巴特沃斯低通滤波器的实数域进行迁移,使其处于2 MHz上,得到带宽为2 MHz的复数带通滤波器。

本节复数滤波器设计步骤如下:

(1) 首先对三阶巴特沃斯低通滤波器进行设计,令其满足复数滤波器设计条件。三阶巴特沃斯低通滤波器通常由一阶低通滤波器与二阶低滤波器级联构成,公式描述如下:

[Ts=1RSsC1+1×1L1C2s2+L2RLs+1] (1)

式中:[RS],[RL]分别用于描述一阶低通滤波器和二阶低通滤波器的电阻;[s]用于描述电阻系数;[C1],[C2]分别用于描述一阶低通滤波器和二阶低通滤波器的电容;[L1],[L2]分别用于描述一阶低通滤波器和二阶低通滤波器的电感。

(2) 通过OTA的低通滤波器结构对一阶和二阶低通滤波器进行设计。本节设计的一阶低通滤波器电路图如图3所示,二阶低通滤波器电路图如图4所示。在进行设计的过程中,需保持传输函数的一致性,为了便于设计,需对相关参数进行改进[6⁃7]。

图3 一阶低通滤波器

图4 二阶低通滤波器

(3) 把有源低通滤波器在实时频率上平移,在LaPlace转换过程中,获取有源复数带通滤波器。

2 实验结果分析

为了验证本文设计的基于CMOS的电子传感接收电路的有效性,需要进行相关的实验分析。实验将FPGA电路和PTAT电路作为对比进行实验测试。

本节对本文设计电路和FPGA电路、PTAT电路进行仿真,将电压增益、噪声指数、输入参考三阶截断点、直流偏置电流和电源电压作为测试指标。

射频放大器的噪声性可通过噪声系数[F]或噪声指数[NF]衡量。噪声系数能够体现放大器信噪比,其可通过放大器输入端信噪比[SNRin]和输出端信噪比[SNRout]之比进行计算,如下:

[F=SNRinSNRout] (2)

噪声指数为噪声系数的对数形式,如下:

[NFdB=10logF] (3)

电压增益[AV]就是放大器输出、输入电压之比,其与[S]参数之间的关系如下:

[AV=V2V1=S211+ΓL1-S22ΓL1+Γin] (4)

式中:[V2]用于描述放大器输出;[V1]用于描述输入电压;[S21]用于描述输入反射系数;[ΓL]用于描述负载反射系数;[S22]用于描述输出反射系统;[Γin]用于描述源反射系数。

输入三阶截断点IIP3的划分情况如下:在射频接收机中,信号经不同模块单元处理,所有单元都会有固定的噪声系数和三阶交调截点,整个射频接收机的噪声系数和三阶截断点是所有模块单元噪声系数与三阶交调截点级联,需对噪声系数与三阶交调截点进行确定,以简化电路结构,达到电路要求。假设各级间相互作用,第一级网络功率增益和噪声系数分别用[G1],[IIP31]进行描述,第二级网络功率增益与噪声系数分别用[G2],[IIP32]进行描述,第三级网络功率增益和噪声系数分别用[G3],[IIP33]进行描述,则输入参考三阶截断点为:

[1IIP3=1IIP31+G1IIP32+G1G2IIP33] (5)

电子传感接收电路主要性能参数设计要求和三种电路的仿真结果如表1所示。

表1 电子传感接收电路主要性能参数设计要求和仿真结果

分析表1可以看出,本文设计电路性能一直符合设计要求,而FPGA电路和PTAT电路的部分性能指数不符合设计要求,说明本文电路性能较高。

3 结 论

本文设计了一种基于CMOS的电子传感接收电路,详细介绍了各模块的设计过程。实验结果表明,所设计电路符合设计要求,性能较高。

参考文献

[1] 骆丽,李瑞菁.基于压缩传感的CMOS图像传感器电路研究[J].北京交通大学学报,2016,40(2):41⁃46.

[2] 李珂,顾飞.基于CMOS工艺的ARINC429总线接收器设计[J].电子与封装,2016,16(3):23⁃25.

[3] 莫宝争.基于CMOS恒跨导运算放大器的设计与研究[J].工业控制计算机,2016,29(5):146⁃147.

[4] 王征,何云丰,曹小涛,等.基于FPGA的大面阵CMOS相机高速率电子学系统设计[J].液晶与显示,2016,31(2):173⁃178.

[5] 农高海.应用于无线传感网的低功耗CMOS温度传感器[J].电子器件,2016,39(4):790⁃795.

[6] 董茂林,周鹏,王传刚.一种接收机AFC电路的设计与实现[J].现代电子技术,2014,37(7):71⁃72.

[7] 纪辉进,凃玉珊,刘荷花.基于软硬协作决策的目标检测传感系统设计与实现[J].现代电子技术,2016,39(8):100⁃103.